# Lecture 22 Cache Examples

#### Lecture 22 - Cache Examples

**17**<sub>10</sub>

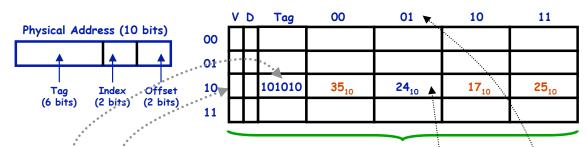

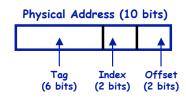

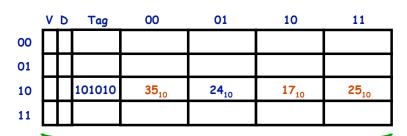

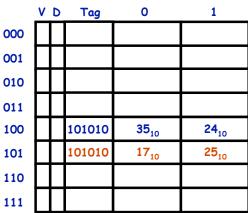

A 4-entry direct mapped cache with 4 data words/block

10

All of these physical addresses

would have the same tag

10

101010

All of these physical addresses map to the same cache entry

2

If we read  $\frac{10}{10}$ 1010 10 01 we want to brindata word  $24_{10}$  into the cache.

Where would this data go? Well, the inde is 10. Therefore, the <u>data word</u> will go somewhere into the 3<sup>rd</sup> <u>block</u> of the cache (make sure you understand terminology)

More specifically, the data word would go into the 2<sup>nd</sup> position within the block - because the offset is '01'

The principle of spatial locality says that if we use one data word, we'll probably use some data words that are close to it - that's why our block size is bigger than one data word. So we fill in the data word entries surrounding 101010 10 01 as well.

#### Lecture 22 - Cache Examples

A 4-entry direct mapped cache with 4 data words/block

- Therefore, if we get this pattern of accesses when we start a new program:

- What happens if we get an access to location: 100011 | 10 | 11 (holding data: 12<sub>10</sub>)

- 1.) 101010 10 00

- 2.) 101010 10 01

- 3.) 101010 10 10

- 4.) 101010 10 11

After we do the read for 101010 10 00 (word #1), we will automatically get the data for words #2, 3 and 4.

What does this mean? Accesses (2), (3), and (4) ARE NOT <u>COMPULSORY</u> <u>MISSES</u>

Index bits tell us we need to look at cache block 10.

So, we need to compare the <u>tag</u> of this address - 100011 - to the tag that associated with the current entry in the cache block - 101010

These DO NOT match. Therefore, the data associated with address 100011 10 11 IS NOT VALI What we have here could be:

- · A compulsory miss

- · (if this is the 1st time the data was accessed)

- · A conflict miss:

- (if the data for address 100011 10 11 was present, but kicked out by 101010 10 00 - for example)

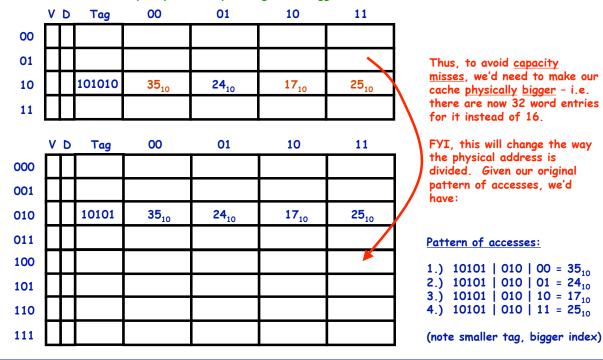

### Lecture 22 - Cache Examples

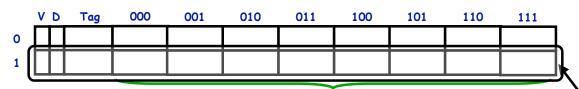

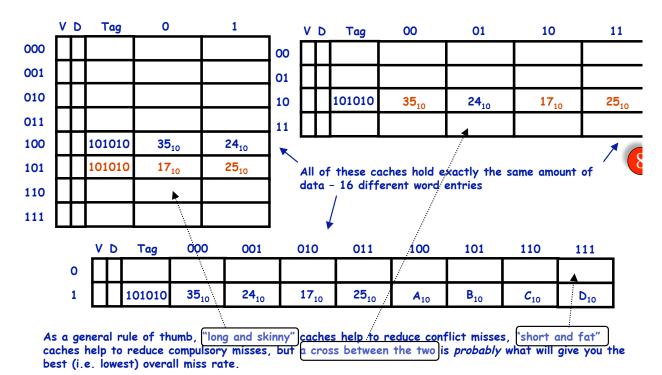

This cache can hold 16 data words...

What if we change the way our cache is laid out - but so that it still has 16 data words? One way we could do this would be as follows:

All of the following are true:

- · This cache still holds 16 words

- · Our block size is bigger therefore this should help with compulsory misses

- · Our physical address will now be divided as follows:

- The number of cache blocks has DECREASED

- · This will INCREASE the # of conflict misses

1 cache

block entr

#### Lecture 22 - Cache Examples

What if we get the same pattern of accesses we had before?

|   | ٧ | D | Tag    | 000                     | 001                     | 010              | 011                     | 100                    | 101             | 110                    | 111                    |

|---|---|---|--------|-------------------------|-------------------------|------------------|-------------------------|------------------------|-----------------|------------------------|------------------------|

| 0 |   |   |        |                         |                         |                  |                         |                        |                 |                        |                        |

| 1 |   |   | 101010 | <b>35</b> <sub>10</sub> | <b>24</b> <sub>10</sub> | 17 <sub>10</sub> | <b>25</b> <sub>10</sub> | <b>A</b> <sub>10</sub> | B <sub>10</sub> | <b>C</b> <sub>10</sub> | <b>D</b> <sub>10</sub> |

|   | _ | _ |        |                         |                         |                  |                         |                        |                 |                        |                        |

Pattern of accesses: (note different # of bits for offset and

Note that there is now more data associated with a given cache block.

101010 1 000 1.) 101010 1 001 2.)

index now)

- 3.) 101010 1 010

- 4.) 101010 1 011

However, now we have only 1 bit of index. Therefore, any address that comes along that has a tag that is different than '101010' and has 1 in the index position is going to result in a conflict miss.

## Lecture 22 - Cache Examples

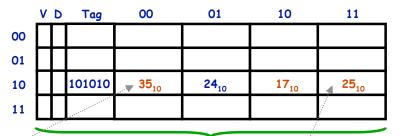

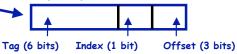

But, we could also make our cache look like this...

There are now just 2 words associated with each cache block.

Again, let's assume we want to read the following data words:

| Tag                                                  | Index | <u>Offset</u> | Address Holds Data      |

|------------------------------------------------------|-------|---------------|-------------------------|

| 1.) 101010                                           | 100   | 1 0           | <b>35</b> <sub>10</sub> |

| <b>2.)</b> 101010                                    | 100   | 1             | <b>24</b> <sub>10</sub> |

| 3.) 101010                                           | 101   | 0             | <b>17</b> <sub>10</sub> |

| 1.) 101010<br>2.) 101010<br>3.) 101010<br>4.) 101010 | 101   | 1             | <b>25</b> <sub>10</sub> |

Assuming that all of these accesses were occurring for the 1st time (and would occur sequentially), accesses (1) and (3) would result in compulsory misses, and accesses would result in hits because of spatial locality. (The final state of the cache is shown after all 4 memory accesses).

Note that by organizing a cache in this way, conflict misses will be reduced. There are now more addresses in the cache that the 10-bit physical address can map too.

#### Lecture 22 - Cache Examples

But what about capacity misses?

## Lecture 22 - Cache Examples

#### What's a capacity miss?

- The cache is only so big. We won't be able to store every block accessed in a program must them swap out!

- · Can avoid capacity misses by making cache bigger